# MECL 10,000 ARITHMETIC ELEMENTS MC10179, MC10180, MC10181

by

Tom Balph

Computer Applications

The MECL 10,000 arithmetic functions include a 4-bit arithmetic unit, a dual adder/subtractor, and a lookahead carry block. This application note describes the devices and shows their operation in larger system configurations.

**MOTOROLA** Semiconductor Products Inc.

## MECL 10,000 ARITHMETIC ELEMENTS MC10179, MC10180, MC10181

## INTRODUCTION

The designer of a high speed digital system may have the need to perform arithmetic operations on binary words. The MECL 10,000 family of integrated circuits has several arithmetic elements among its many versatile functions. These include the MC10180 dual adder/subtractor, the MC10181 4-bit arithmetic logic unit/function generator, and the MC10179 lookahead carry block.

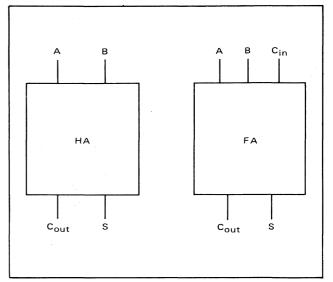

Arithmetic operations on binary numbers use two basic single-bit computing elements. These elements are the full adder (FA) and the half adder (HA). To describe the adders use the following nomenclature:

A = augend

B = addend

S = sum

Cin = input carry

$C_{out} = output carry$

The more basic element is the half adder. It is just a two input element producing the sum and output carry of the augend and addend. (The augend and addend are the two bits being added together). The adder equations are:

$$S = A \oplus B = A\overline{B} + \overline{B}A \tag{1}$$

$$C_{\text{out}} = A \cdot B \tag{2}$$

If the half adder is extended to include the addition of an input carry, the result will be the full adder. The FA adds augend, addend, and input carry producing sum and output carry. The FA equations are:

$$S = A \oplus B \oplus C_{in} = \overline{C}_{in}(A\overline{B} + \overline{A}B) + C_{in}(AB + \overline{A}\overline{B})$$

(3)

$$C_{out} = (AB) + (AC_{in}) + (BC_{in})$$

(4)

The symbolic representations of the HA and FA are shown in Figure 1. These two adders are the basic configurations around which the MECL arithmetic elements are designed. Addition and subtraction along with variations on both use the FA and HA as the basic computational tool.

It is interesting to note an unusual feature of the full adder equations. The sum and output carry equations are the same in positive and negative logic. If the sum

FIGURE 1 — Symbolic representations of the half adder and full adder.

equation is known in positive logic (i.e., the more positive level is a "one" or true state), the negative logic equation can be found. Using the same variable assignments, to convert to negative logic (i.e., the less positive level is a "one" or true state), substitute the complements of the variables into the equation. Equation (3) becomes in negative logic:

$$\overline{S} = C_{in} (\overline{A}B + A\overline{B}) + \overline{C}_{in} (\overline{A}\overline{B} + AB)$$

(5)

Addendum "A" demonstrates the development of equation (5) to

$$S = \overline{C}_{in} (A\overline{B} + \overline{A}B) + C_{in} (AB + \overline{B}\overline{A})$$

Which equates to the original sum equation in positive logic.

For the carry-out equation, the negative logic equation becomes:

$$\overline{C}_{Out} = \overline{C}_{in}\overline{A} + \overline{C}_{in}\overline{B} + \overline{A}\overline{B}$$

(6)

after substituting the complements of the variables.

Simplifying equation (6) as in Addendum "B" yields

$$C_{out} = C_{in} A + C_{in}B + AB$$

Circuit diagrams external to Motorola products are included as a means of illustrating typical semiconductor applications; consequently, complete information sufficient for construction purposes is not necessarily given. The information in this Application Note has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described any license under the patent rights of Motorola Inc. or others.

Equation (6) is the same as (4) therefore, the positive and negative logic equations for  $C_{\rm Out}$  are the same. This result will be used later on to describe the MECL 10,000 arithmetic elements in both logic definitions.

The MC10180, MC10181, and MC10179 each have different capabilities. The following device descriptions will explain operation of each device.

## Device Description

#### MC10180

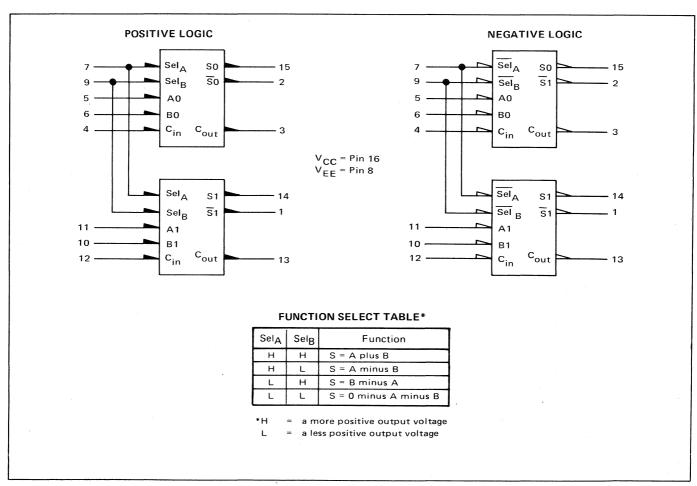

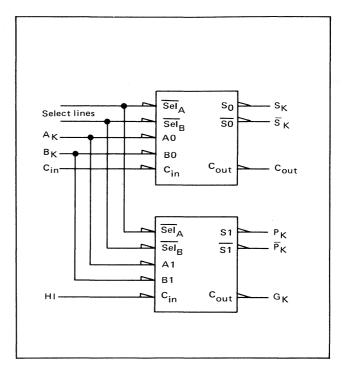

The MC10180 is a dual full adder/subtractor. Each adder is provided with inputs of operand A, operand B, (operand refers to the binary word being added or subtracted) and carry-in and with outputs of sum, sum, and carry out. The add/subtract operation is determined by two select lines common to each adder. The mode of operation is selected as shown in Figure 2 which provides the block diagram and function select table for the MC10180.

In examining operation of the device more closely (Figure 3), the configuration is logically a full adder with an exclusive-NOR function on operand A and on operand B. Either operand may be selectively inverted or rippled-through to the adder. In this manner, the subtraction of either operand can be provided.

The positive logic equations for the MC10180 are:

$$S = \overline{C}_{in}(\overline{A}'B' + A'\overline{B}') + C_{in}(A'B' + \overline{A}'\overline{B}')$$

(7)

$$C_{out} = C_{in}A' + C_{in}B' + A'B'$$

(8)

where

$$A' = A \oplus Sel_A = A \odot Sel_A \tag{9}$$

$$B' = B \oplus Sel_B = B \odot Sel_B \tag{10}$$

Equations (7) and (8) are for the sum and carry-out of the full adder in terms of  $C_{in}$ , A', and B'. A' and B' are the operands A and B modified by the exclusive-NOR function.

It was shown that the full adder equations are similar in both logic definitions. Because the positive and negative logic equations for the FA are the same, the MC10180 may be used similarly in both logic definitions. However, the negative logic equations for A' and B' must become:

$$A' = A \oplus \overline{Sel_A} = A \odot Sel_A \tag{11}$$

$$B' = B \oplus \overline{Sel_B} = B \odot Sel_A \tag{12}$$

FIGURE 2 - Block diagram and function select table for MC10180.

FIGURE 3 - Positive Logic Diagram for MC10180

The exclusive-NOR function becomes an exclusive-OR function in negative logic. Therefore, the select lines are redefined to  $\overline{Sel_A}$  and  $\overline{Sel_B}$  for negative logic. Equations (7) and (8) still hold.

## MC10181

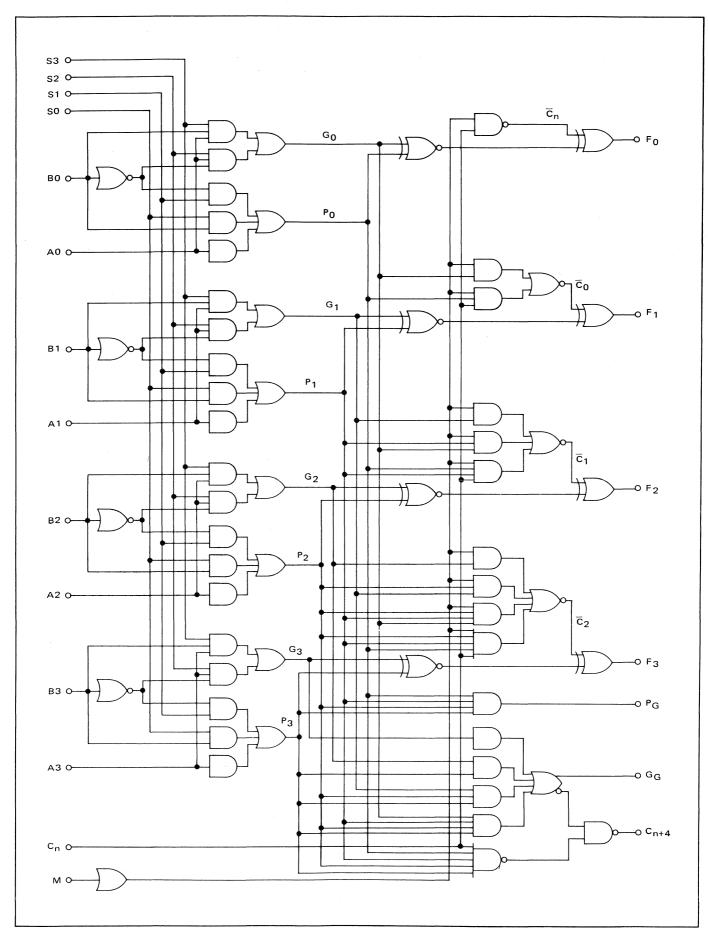

The MC10181 is a more complex device than the MC10180. The MC10181 is an arithmetic logic unit capable of performing 16 logic operations and 16 arithmetic operations on two 4-bit operands (Figure 4). It has inputs for a 4-bit operand A, a 4-bit operand B, and carry-in and has outputs for a 4-bit function-out, carry-out, and group carry propagate and carry generate.

The logic or arithmetic operation of the ALU is determined by internal logic controlled by the mode input. In the arithmetic mode, full internal lookahead carry is incorporated to determine the 4-bit function-out and carry-out. The mode control disables the internal carry circuitry for logic mode operation, and carry is ignored. In the logic mode, the function-out is generated on a bit per bit basis.

Each mode of operation has 16 function capability (32 total). The four select lines (S<sub>0</sub> through S<sub>3</sub>) determine which function will be performed on operands A and B in either mode of operation.

When the mode control is in the more positive (high) logic state, the MC10181 is in the logic mode of operation and can perform any of 16 possible logic operations on two variables. These functions are especially useful for computer processor applications where the processor must execute commands such as generation of all 1's or 0's,

"mask" the contents of a register, OR or AND the contents of two registers, or similar logic operations.

The arithmetic mode is also composed of 16 functions. These functions perform various forms of addition and subtraction on operands A and B. The different functions are useful for a variety of operations. As examples, the A times 2 function may be used for an arithmetic shift in a processor, the A minus 1 function may do a decrement operation, the two's complement of minus 1 may be generated, and the A plus 0 function may either ripplethrough word A or increment word A by adding a carry-in.

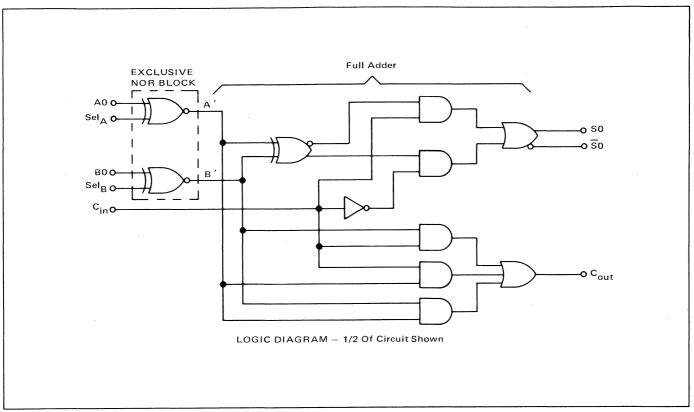

The operation of the device may be seen more clearly by examining the negative logic diagram of Figure 4A. For each bit, two internal functions may be defined:

$$G_i = (S_2 A_i \overline{B}_i) + (S_3 A_i B_i)$$

(13)

$$P_i = A_i + S_0 B_i + S_i \overline{B}_i \tag{14}$$

where i = 0 through 3.  $G_i$  and  $P_i$  are the operands A and B modified by the  $S_0$ ,  $S_1$ ,  $S_2$ , and  $S_3$  control lines. The two functions are independent of the mode control and hold for both modes of operation.

The function-out is then written in terms of  $G_i$ ,  $P_i$ , and carry. In the logic mode (M = high state), the function-out is dependent only on  $G_i$  and  $P_i$  as the carry logic is disabled. The negative logic equation for function-out becomes:

$$F_{i} = \overline{(G_{i} \oplus P_{i})} = G_{i} \odot P_{i} \tag{15}$$

FIGURE 4A - MC10181 NEGATIVE LOGIC DIAGRAM

For arithmetic operation the internal lookahead carry is not inhibited. The equation then becomes:

$$F_{i} = \overline{(G_{i} \oplus P_{i})} \oplus \overline{C}_{i-1} \tag{16}$$

where

$$\overline{C}_{i-1} = \overline{G}_{i-1} + (P_{i-1} C_{i-2})$$

(17)

Equation (17) is the expression for carry in terms of lookahead techniques. Lookahead techniques may be extended to secondary levels beyond the basic MC10181. The group carry propagate and carry generate are provided for this purpose to be used with the MC10179. That is:

$$P_G = P_0 P_1 P_2 P_3$$

(18)

$$G_G = G_3 + P_3G_2 + P_3P_2G_1 + P_3P_2P_1G_0$$

(19)

$$C_{n+4} = G_G + P_3 P_2 P_1 P_0 C_n \tag{20}$$

Secondary lookahead with the MC10179 can significantly reduce add times on long words. More will be said later on lookahead carry arithmetic.

The MC10181 has been described in terms of negative logic. For positive logic operation, the functions become altered as shown in Figure 4B. The 16 functions for logic operation are altered due to the redefinition in logic levels. However, arithmetic operation is somewhat similar in positive and negative logic. The differences in the arithmetic functions are due to the logical expressions contained within arithmetic equations.

To show this, use the conditions of  $S_0 = H$ ,  $S_1 = H$ ,  $S_2 = H$ ,  $S_3 = L$ , and M = L. The arithmetic expression for negative logic is:

$$F = A plus (A \cdot B)$$

The equivalent arithmetic function in positive logic is:

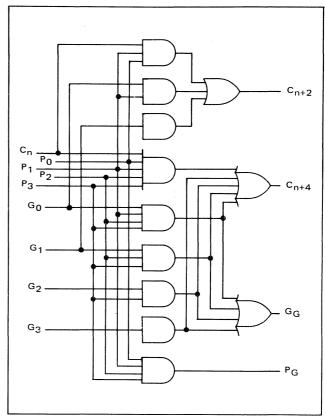

FIGURE 5 - Negative Logic Diagram for MC10179.

$$F = A plus (A + B)$$

The only difference in the two functions is that the logical expression  $A \cdot B$  changes to A + B.

## MC10179

The MC10179 is a logic block that performs the lookahead carry function for the previously described MC10180 and MC10181. The carry generate and carry propagate inputs are used to produce carry outputs external to the adders. The simultaneous production of

| Function Select<br>\$3 \$2 \$1 \$0 |   |   |    | Logic Functions<br>M is High C = D.C.<br>F | Arithmetic Operation<br>M is Low C <sub>n</sub> is low<br>F |  |  |

|------------------------------------|---|---|----|--------------------------------------------|-------------------------------------------------------------|--|--|

| L                                  | L | L | L  | F=Ā                                        | F = A                                                       |  |  |

| L                                  | L | L | н  | F. = Ā + B                                 | F = A plus (A ● B)                                          |  |  |

| L                                  | L | Н | L  | F = A + B                                  | F = A plus (A ● B)                                          |  |  |

| L                                  | L | Н | н  | F = Logical "1"                            | F = A times 2                                               |  |  |

| L                                  | н | L | L  | F = Ā ● B                                  | F = (A + B) plus 0                                          |  |  |

| L                                  | Н | L | Н  | F = B                                      | F = (A + B) plus (A ● B)                                    |  |  |

| L                                  | Н | Н | L  | F=A 📵 B                                    | F = A plus B                                                |  |  |

| L                                  | н | н | Н  | F = A + B                                  | F = A plus (A + B*)                                         |  |  |

| Н                                  | L | L | L  | - F = Ā ● B                                | $F = (A + \overline{B}) \text{ plus } 0$                    |  |  |

| Н                                  | L | L | Н  | F = A + B                                  | F = A minus B minus 1                                       |  |  |

| Н                                  | L | Н | L  | F=B                                        | F = (A + B) plus (A ● B)                                    |  |  |

| Н                                  | L | Н | н  | F = A + B                                  | $F = A plus (A + \overline{B})$                             |  |  |

| н                                  | н | L | L  | F = Logical "0"                            | F = minus 1 (two's complement                               |  |  |

| н                                  | н | L | Η, | F = A ● B                                  | F = (A ● B) minus 1                                         |  |  |

| н                                  | н | н | L  | F = A ● B                                  | F = (A • B) minus 1                                         |  |  |

| н                                  | н | Н | н  | F = A                                      | F = A minus 1                                               |  |  |

|    | nctio |    |    | Logic Functions<br>M is High | Arithmetic Operation  M is Low Cn of LSB must be High |  |  |

|----|-------|----|----|------------------------------|-------------------------------------------------------|--|--|

| S3 | S2    | S1 | S0 | ·F                           | F                                                     |  |  |

| L  | L     | L  | L  | . F = Ā                      | F = A minus 1                                         |  |  |

| L  | L     | L  | Н  | F = A + B                    | F = A plus (A + B)                                    |  |  |

| L  | L     | Н  | L  | F≖Ā∙B                        | F = A plus (A + B)                                    |  |  |

| L  | L     | Н  | Н  | F = Logical "0"              | F = A times 2                                         |  |  |

| L  | Н     | L  | L  | F = A • B                    | F = (A • B) minus 1                                   |  |  |

| L  | Н     | L  | H  | F = B                        | F = (A • B) plus (A + B)                              |  |  |

| L  | Н     | Н  | L  | F = A ⊕ B                    | F = A plus B                                          |  |  |

| L. | Н     | Н  | н  | F = A • B                    | F = A plus (A • B)                                    |  |  |

| H  | L     | L  | L  | F = Ā + B                    | F = (A • B) minus 1                                   |  |  |

| H  | L.    | L  | Н  | F≔A⊙B                        | F = A minus B minus 1                                 |  |  |

| H  | L     | Н  | L. | F = B                        | F = (A • B) plus (A + B)                              |  |  |

| Н  | L     | Н  | Н  | F = A • B                    | F = (A • B) plus A                                    |  |  |

| Н  | Н     | L  | L  | F = Logical "1"              | F = minus 1 (two's complement)                        |  |  |

| Н  | Н     | L  | Н  | F = A + B                    | F = (A + B) plus 0                                    |  |  |

| н  | Н     | Н  | L  | F = A + B                    | F = (A + B) plus 0                                    |  |  |

| н  | Н     | Н  | н  | F = A                        | F = A plus 0                                          |  |  |

**NEGATIVE LOGIC**

FIGURE 4B - MC10181 Function Select Table

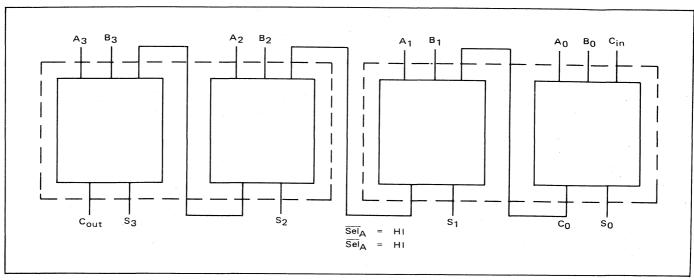

FIGURE 6 - A ripple 4-bit parallel binary adder using two MC10180's.

carry external to the adder greatly reduces add times on long words. Techniques will be shown using both the MC10180 and the MC10181 with the MC10179. The logic diagram of the MC10179 is shown in Figure 5.

The negative logic equations for the MC10179 are:

$$P_{G} = P_{0}P_{1}P_{2}P_{3} \tag{21}$$

$$G_G = (G_0P_1P_2P_3) + (G_1P_2P_3) + (G_2P_3) + G_3$$

(22)

$$C_{n+2} = (C_n P_0 P_1) + (G_0 P_1) + G_1$$

(23)

$$C_{n+4} = (C_{1}P_{0}P_{1}P_{2}P_{3}) + (G_{0}P_{1}P_{2}P_{3}) + (G_{1}P_{2}P_{3}) + (G_{2}P_{3}) + (G_{2}P_{3}) + G_{3}$$

(24)

Although the device has been shown in terms of negative logic, the MC10179 may also be used in terms of positive logic definition. The lookahead carry adders shown in the application note apply for both logic definitions.

### PARALLEL ADDERS

A parallel binary adder is used to sum two numbers of n bits. A parallel adder requires n full adders for two n-bit numbers if carry is rippled between adders. Figure 6 illustrates this technique using the MC10180.

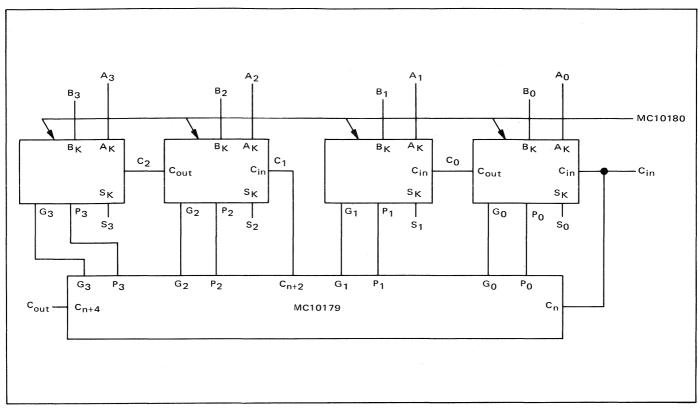

The MC10181 may also be used rippling carry between devices. The MC10181 is basically a parallel arithmetic block, 4 bits wide. The device can be used as a parallel adder with carry rippled between devices (every 4 bits). Figure 7 shows this technique.

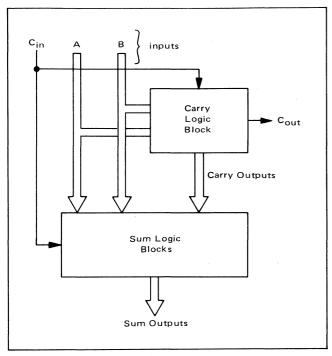

Another type of parallel adder is the carry lookahead configuration. The basic principle of lookahead addition is the examination of the inputs of each adder stage and the simultaneous production of the proper carries for each of the stages. The overall add time can be significantly reduced from that of a ripple adder.

In a simple block form, the lookahead adder is shown in Figure 8. The group of input bits (number A and number B) is applied to the carry logic block together with the initial carry. The carry outputs are then provided

FIGURE 7 - An 8-bit parallel adder using the MC10181 with carry rippled between devices.

FIGURE 8 - Carry lookahead adder in block form.

to the sum logic blocks to form the proper sum outputs.

Two new symbols are defined for carry lookahead addition:

$$G_{K} = A_{K} \cdot B_{K} \tag{25}$$

$$P_{K} = A_{K} \oplus B_{K} \tag{26}$$

$G_K$  is the symbol for the carry output bit generated at the Kth bit position and is called the carry generate. The carry generate is produced only when there is a true input on both the  $A_K$  and  $B_K$  inputs.  $P_K$  is the symbol for propagate, which indicates that a carry will be produced if there is a true input on the  $A_K$  or the  $B_K$  lines and a carry is present from the previous stage. Notice that the equations for  $G_K$  and  $P_K$  are equivalent to the HA sum and output carry equations.

At the Kth bit position, a carry bit will be generated according to the equation:

$$C_K = G_K + (P_K C_{K-1})$$

(27)

where  $C_{K-1}$  is the carry from the previous stage. This equation may be expanded in terms of the carry input to the parallel adder:

$$C_K = G_K + (P_K G_{K-1}) + (P_K P_{K-1} G_{K-2}) + \dots$$

$\dots + (P_K P_{K-1} P_{K-2} \dots P_1 G_0)$  (28)

where  $G_0 = C_{in}$  (initial carry in)

The carry at each stage of the parallel adder can then

FIGURE 9 — MC10180 connected as a fast carry adder, producing carry propagate and carry generate.

be produced as a combination of propagate and generate terms. The carry need not ripple through each stage of adder.

The sum block for each sum bit must add an input carry, augend, and addend. The sum equation is:

$$S_{K} = A_{K} \oplus B_{K} \oplus C_{K-1}$$

(29)

which is equivalent to the sum equation of the FA.

## LOOKAHEAD ADDITION WITH THE MC10180

It is observed that equations (25) and (26) for GK and PK are equivalent to equations (1) and (2) for output carry and sum for the HA. It can also be observed that equations (3) and (4) for the FA reduce to equations (1) and (2) for the HA if input carry is held to the zero state. Therefore, a full adder can be used to produce GK and PK for the associated addend and augend bits.

A fast carry adder for lookahead addition can then be made utilizing the MC10180. One half of the dual adder is used as a summing block, and one half of the device is used to produce carry generate and carry propagate. Figure 9 illustrates this technique.

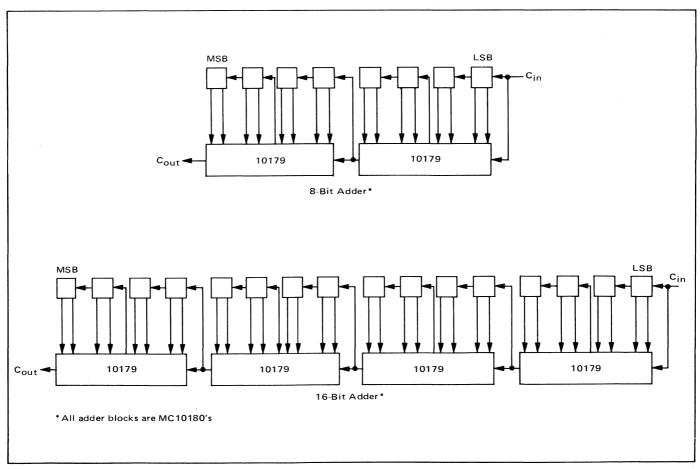

A 4-bit parallel lookahead carry adder may be connected as shown in Figure 10 using the MC10180 and the MC10179. The MC10179 generates carry every second bit, therefore carry is rippled between every other adder.

For longer adders the basic 4-bit configuration of Figure 10 would be repeated. Figure 11 shows simplified block diagrams of 8-bit and 16-bit configurations.

Carry lookahead may be extended to higher levels by using the group generate and group propagate outputs of the MC10179 to produce carry at a secondary level. This

FIGURE 10 — A 4-bit parallel lookahead carry adder using the MC10179 and MC10180's (connected as in Figure 9).

FIGURE 11 - Block diagrams of 8-bit and 16-bit lookahead carry adders using the MC10180 and MC10179

technique gains a time advantage only with word lengths above 16 bits.

The adders shown using the MC10180 are not as fast or as efficient in package count as adders using the MC10181. The advantage of using the MC10180 is that carry is available for each adder bit. Also, the MC10180 is in the 16-pin dual-in-line package for PC board layouts that cannot use the 24-pin package required by the MC10181.

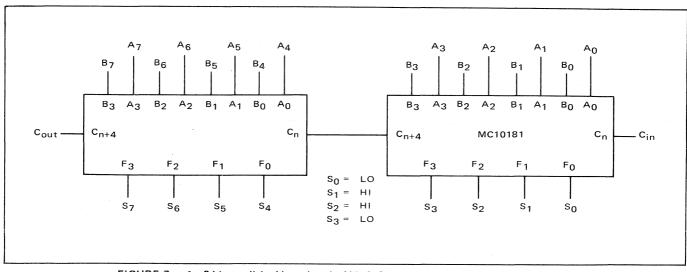

## **LOOKAHEAD ADDITION WITH THE MC10181**

The MC10181 uses lookahead carry internal to the device to do arithmetic operations. In the arithmetic mode of operation for addition of A and B (S0 = L, S1 = H, S2 = H, S3 = L), equations (13) and (14) become:

$$G_i = A_i \cdot B_i \tag{30}$$

$$P_i = A_i + B_i \tag{31}$$

Equation (30) is the same as equation (25) for  $G_K$ , although equation (31) differs from equation (26) for  $P_K$ .

It can be shown that equation (31) contains the set of terms of equation (26) and therefore produces carry propagate (although function A + B contains a redundant term). The propagate and generate functions are then used to sum operands A and B and input carry. The internal carry is formed using lookahead logic as shown by equation (17).

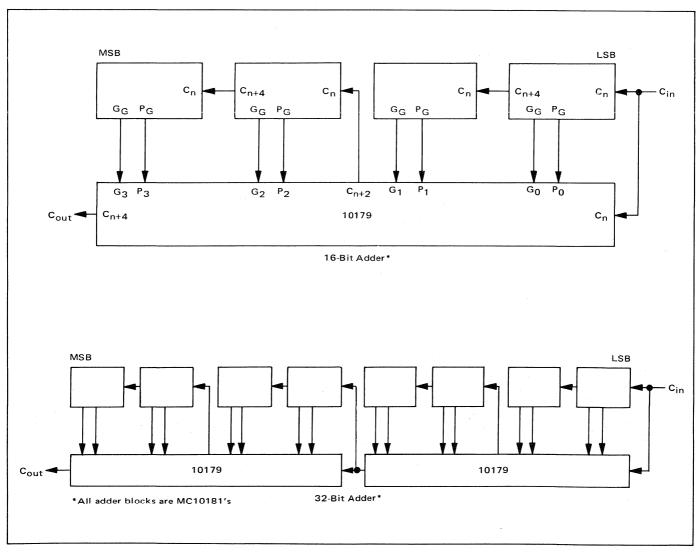

The MC10181 with internal lookahead adders is in itself a very fast arithmetic unit. When the MC10181 is incorporated with the MC10179 even faster performance is possible for long words. Use of the MC10179 is advantageous for word lengths longer than 16 bits.

The MC10179 in this application performs secondary level lookahead as the MC10181 performs the first level internally. The group propagate and group generate outputs are utilized by the MC10179 to produce the carry out. Block diagrams of 16-bit and 32-bit adders with the MC10181 and MC10179 are shown in Figure 12.

## COMPARISON OF ADDER PERFORMANCE

Several parallel adder configurations have been shown using the MC10180 and MC10181. Figure 13 gives a table

FIGURE 12 - Block diagrams of 16-bit and 32-bit lookahead carry adders using the MC10181 and MC10179

| No.     | Configuration          | Total           | Package Count |         |         |

|---------|------------------------|-----------------|---------------|---------|---------|

| of Bits | Configuration          | Add Time (nsec) | MC10179       | MC10180 | MC10181 |

| 4       | Ripple<br>Ripple       | 11 8            |               | 2       | 1       |

|         | Lookahead              | 12              | 1             | 4       | 1       |

| 8       | Ripple                 | 20              |               | 4       |         |

|         | Ripple<br>Lookahead    | 11<br>15        | 2             | 8       | 2       |

| 16      | Riple                  | 38              |               | 8       |         |

|         | Ripple<br>Lookahead    | 17 21           |               | 10      | 4       |

|         | Lookahead              | 16              | 1             | 16      | 4       |

| 24      | Ripple                 | 55              |               | 12      |         |

|         | Ripple                 | 23              |               |         | 6       |

|         | Lookahead<br>Lookahead | 22<br>16        | 7             | 24      | 6       |

| 32      | Ripple                 | 73              |               | 16      |         |

|         | Ripple                 | 30              |               |         | 8       |

|         | Lookahead              | 25              | 10            | 32      |         |

|         | Lookahead              | 19              | 2             |         | 8       |

| 64      | Ripple                 | 132             |               | 32      |         |

|         | Ripple<br>Lookahead    | 54              | 20            |         | 16      |

|         | Lookahead              | 31<br>25        | 20<br>4       | 64      | 16      |

FIGURE 13 — Typical add times for various parallel adders using the MC10180, MC10181, and MC10179.

of typical addition times for these techniques for various bit lengths. The trade-offs of different types of parallel adders will determine which adder is best for a particular application.

The adders using the MC10180 have the advantage of access to each individual carry bit. The disadvantages of the MC10180 adders are increased package count and longer add times.

The MC10181 has the highest performance in any parallel technique (both ripple and lookahead) at minimum package count. This is due to the internal lookahead carry and 4-bit capability of the device.

## SIGNED 2'S COMPLEMENT ARITHMETIC

The binary adders described can be used also for signed 2's complement arithmetic including addition and subtraction. Subtraction is performed by the addition of the 2's complement of the subtrahend to the minuend (for A-B, A = minuend and B = subtrahend). The 2's complement of a number is found by inverting the number bits and adding one to the number, that is, the 2's complement of  $B = \overline{B}$  plus 1.

The MC10180 and MC10181 can also perform parallel subtraction. In either case, the subtrahend (normally word B) is inverted by use of the control lines to the device. The  $C_{in}$  to the adder is then forced to a "1" state, and subtraction is performed by addition of the 2's complement of the number.

The MC10180 also has the ability to invert either operand A or B. In this manner, various operations as A-B, B-A, or -A-B may be performed with the basic adder configuration.

The MC10181 is more versatile in the arithmetic configuration than just for addition or subtraction. Many variations on A + B or A-B can be performed with the 16 arithmetic function capability of the device. Such functions as A minus 1, A plus 0, and A times 2 (A plus A) are useful for implementing various computer instructions. Also, as mentioned earlier arithmetic functions containing logical expressions (F = A plus (A + B)) may prove useful in particular applications.

### **CONCLUSION**

The MC10180, MC10181, and MC10179 are versatile building blocks that may be used in a variety of arithmetic operations. The devices have different advantages that determine which is most suitable for a particular application.

The MC10181 has 32 function capability, is 4-bits wide, is very fast, and comes in a 24-pin package. The characteristic of the device that may be detrimental to some applications is that the internal carry bits are not available for use.

The MC10180 is a fast dual adder. Its advantages lie in applications where single bit adders are useful. These applications include serial adders and parallel adders where the individual carry bits must be available. The device also is in a 16-pin package. When compared to configurations using the MC10181, the MC10180 adder will be slower and requires a higher package count.

The MC10179 lookahead carry block may be used in configurations with both the MC10180 and MC10181. Addition time on long words can be reduced significantly using this device with the MECL 10,000 adders.

## ADDENDUM "A"

(5)

$$\overline{S} = C_{in} (\overline{A}B + A\overline{B}) + \overline{C}_{in} (\overline{A}\overline{B} + AB)$$

$$S = \overline{C}_{in} (A\overline{B} + \overline{A}B) + C_{in}(AB + \overline{B}\overline{A})$$

$S = C_{in}(\overline{A}B + A\overline{B}) + \overline{C}_{in}(\overline{A}\overline{B} + AB)$

## ADDENDUM "B"

$$S = \left[\overline{C}_{in} + \left[ (A + \overline{B}) \cdot (\overline{A} + B) \right] \right] \cdot \left[ C_{in} + \left[ (A + B) \cdot (\overline{A} + \overline{B}) \right] \right]$$

$$\overline{C}_{out} = \overline{C}_{in} \overline{A} + \overline{C}_{in} \overline{B} + \overline{A} \overline{B}$$

$$\overline{C}_{out} = \overline{C}_{in} \overline{A} + \overline{C}_{in} \overline{B} + \overline{A} \overline{B}$$

The equation becomes

$$S = \left[\overline{C}_{in} + (A\overline{A} + AB + \overline{B}\overline{A} + B\overline{B})\right] \cdot \left[C_{in} + (A\overline{A} + A\overline{B} + B\overline{A} + B\overline{B})\right]$$

$$C_{out} = (C_{in} + A)(C_{in} + B)(A + B)$$

$$S = \left[\overline{C}_{in} + (AB + \overline{B}\overline{A})\right] \cdot \left[C_{in} + (A\overline{B} + \overline{A}B)\right]$$

$$C_{out} = (C_{in} + C_{in} B + C_{in}A + AB)(A + B)$$

$$S = \overline{C}_{in}C_{in} + \overline{C}_{in} (A\overline{B} + \overline{A}B) + C_{in} (AB + \overline{B}\overline{A})$$

$$+ (AB + \overline{B}\overline{A}) (A\overline{B} + \overline{A}B)$$

$$C_{out} = C_{in}A + C_{in}AB + C_{in}A + AB + C_{in}B + C_{in}B + C_{in}AB + AB$$

Noting that:

$$C_{out} = C_{in}A + C_{in}AB + C_{in}B + AB$$

$$(AB + \overline{B}\overline{A}) (A\overline{B} + \overline{A}B) = (A \circ B) (A \oplus B) =$$

$$(A \circ B) \overline{(A \circ B)} = 0$$

$C_{out} = C_{in}A + C_{in}B + AB$  (6)

### REFERENCES

- 1. "MECL Integrated Circuits Data Book," Motorola Inc., November, 1972.

- 2. "MECL System Design Handbook," Motorola Inc., 2nd Edition, December, 1972.

- 3. AN-488, "High-Speed Addition Using Lookahead Carry Techniques," Motorola, 1969.

- 4. Y. Chu, "Digital Computer Design Fundamentals," New York, McGraw-Hill, 1962.

- 5. I. Flores, "The Logic of Computer Arithmetic," New Jersey, Prentice-Hall, 1963.